A medida que nos acercamos a los límites de la miniaturización en el silicio, los principales fabricantes de procesadores deben encontrar la manera de seguir optimizando la tecnología actual, compensar con una mayor superficie, y por supuesto, explorar nuevos métodos que habiliten el acceso a nodos aún más pequeños. Este último punto nos deja a las puertas de IBM, que acaba de presentar el primer chip de 5 nanómetros en el mundo, creado con un nuevo tipo de transistor, y la aplicación de litografía avanzada.

Cualquier usuario que desee verificar la tecnología utilizada para fabricar al procesador dentro de su ordenador sólo debe descargar una herramienta como CPU-Z o equivalente. La relación entre el nodo y la generación de un procesador ya no es tan estrecha, en especial desde que Intel utilizó a los 14 nanómetros en Broadwell, Skylake, y Kaby Lake, con todo listo para repetir la fórmula sobre Coffee Lake. El gigante de Santa Clara insiste en que la arquitectura Cannonlake de 10 nanómetros debutará antes de fin de año, pero los últimos desarrollos en hardware demostraron que su posición no es tan robusta como parecía al principio. El atajo popular en estos días es colocar una mayor cantidad de núcleos en cada chip, sin embargo, el deseo de empujar más abajo al silicio se mantiene firme. Y así llegamos a la última novedad de IBM, que básicamente cortó el número de nanómetros a la mitad.

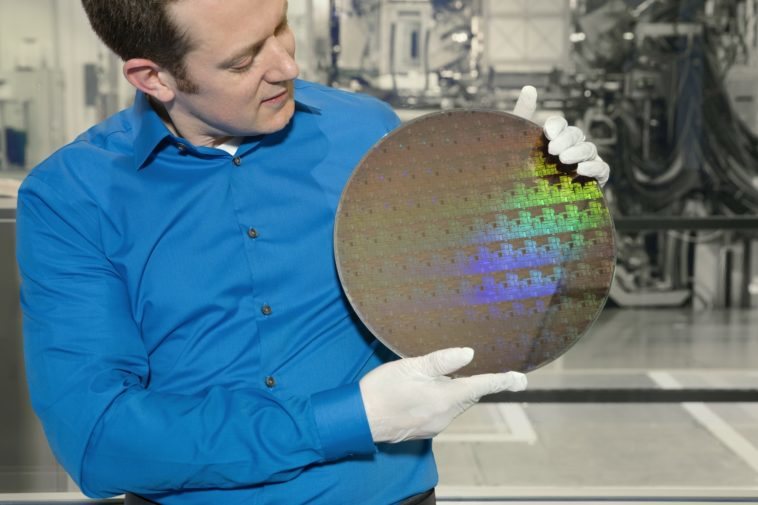

El Gigante Azul unió fuerzas con Samsung y GlobalFoundries para crear el primer chip de silicio fabricado en 5 nanómetros. ¿Cómo lograron esto? Por un lado, utiliza litografía de radiación ultravioleta extrema, algo que IBM ya había evaluado cuando fabricó a su chip de 7 nanómetros en 2015, y por el otro, encontramos un nuevo tipo de transistor. IBM dejó a un lado a los FinFET de triple puerta para enfocarse en el siguiente salto evolutivo, que son los transistores gate-all-around o GAAFET. En términos sencillos, mientras que el diseño FinFET de triple puerta cubre a la aleta de silicio (o la región del canal, si así lo prefieren) en tres puntos, el GAAFET la envuelve por completo, o sea que ya no podemos llamarla aleta, sino que estamos ante nanocables de silicio. Lo más interesante es que IBM no usó a los nanocables de manera vertical: Las imágenes los muestran a 90 grados.

Ahora, ¿cómo convertimos este impresionante avance en números? IBM ya se encargó de eso al hablar de un aumento en el rendimiento del 40 por ciento bajo el mismo consumo (será interesante ver los límites en la disipación de calor), o lo que puede ser más llamativo para ciertos mercados, el mismo rendimiento con una reducción en el uso de energía del 75 por ciento. Otro valor que merece ser destacado es el de la densidad. De ser necesario, IBM podría colocar 30 mil millones de transistores en apenas 50 milímetros cuadrados.